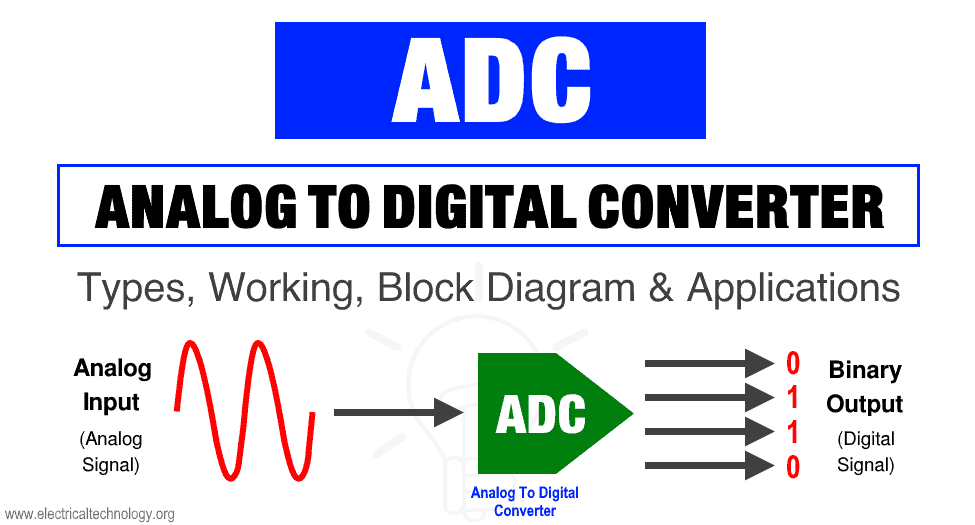

A block diagram of the ADC is shown in Figure 107. The ADC contains a Sample and Hold circuit which ensures that the input voltage to theĪDC is held at a constant level during conversion. If 200x gain is used, 7-bit resolution can be expected. If 1x or 10x gain is used, 8-bit resolution can be expected. Seven differential analog input channels share a common negative terminal (ADC1), while any other ADC input can be selected as the positive input terminal. Two of the differential inputs (ADC1, ADC0 and ADC3, ADC2) are equipped with a programmable gain stage, providing amplification steps of 0 dB (1x), 20 dB (10x), or 46 dB (200x) on the differential input voltage before the A/D conversion. The device also supports 16 differential voltage input combinations. The single-ended voltage inputs refer to 0 V (GND). The ADC is connected to an 8-channel Analog Multiplexer which allows 8 single-ended voltage inputs constructed from the pins of Port F. The ATmega128 features a 10-bit successive approximation ADC.

#Analog to digital converter chip serial#

2-wire Serial Interface Characteristics.Simple Assembly Code Example for a Boot Loader.

#Analog to digital converter chip software#

0 kommentar(er)

0 kommentar(er)